4KB RANDOM READ/WRITE

In order to properly test random 4KB performance we first secure erase to get it in a clean state. Next, the drive is filled by sequentially writing to the RAW NAND capacity twice. We then precondition the drive with 4KB random writes at QD256 until the drive is in a steady state. Finally, we cycle through QD1-256 for 5 minutes each for writes and then reads. All this is scripted to run with no breaks in between. The last hour of preconditioning, the average IOPS, and average latency for each QD is graphed below.

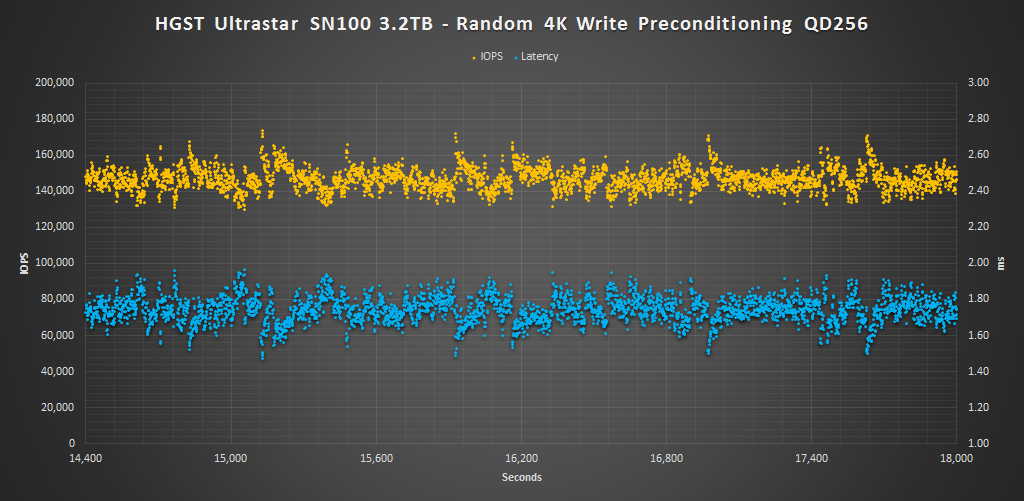

Over the course of our 4KB preconditioning we can see latency consistency ranges about 0.4ms which results in about 40K IOPS distribution ranging from 130K-170K IOPS. The majority of IOPS are around 140-150K and for the most part the minimum 4KB write IOPS are around the 140K rating.

Next we are looking at average IOPS per queue depth. The Ultrastar SN100’s performance consistently increases exponentially up to QD128. At QD256 performance peaks, reaching about 736K read IOPS, which is very close to it’s 743K IOPS rating.

For 4KB read latency per queue depth we can see that it is very well managed up to QD64, where most values are 0.15ms or less and it has a distinct advantage over the Intel up until then. At QD128 and QD256 latency starts to nearly double and reaches 0.34ms.

Next we are looking at average write IOPS per QD. The SN100 shows a steep ramp up in performance from QD1-8 which even surpasses the Intel DC P3608 up until QD64, which is very nice to see. At QD128 and QD256 the Intel SSD takes the lead over the SN100. Performance maxes out at 149K IOPS, which is 9K over its official rating. Write latency is also well managed with latency being under 0.25ms up to QD32. By QD256 latency climbs slightly higher than that of the Intel to 1.72ms.

The SSD Review The Worlds Dedicated SSD Education and Review Resource |

The SSD Review The Worlds Dedicated SSD Education and Review Resource |